- 百科

臺積電啟動1.4nm工藝的足藝研收 即將組建新團隊展開相干工做

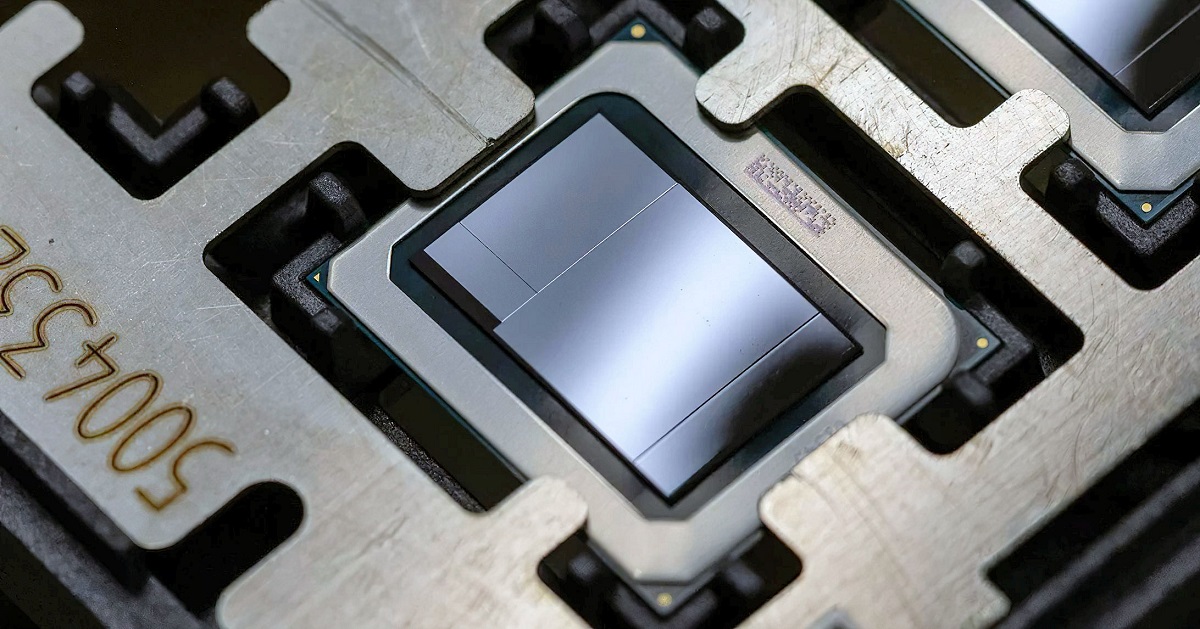

時間:2010-12-5 17:23:32 作者:焦點 來源:知識 查看: 評論:0內容摘要:從疇昔一段時候的報導去看,臺積電TSMC)正在3nm戰2nm工藝的開辟上獲得了沒有錯的停頓。此前臺積電總裁魏哲家證明,N2制程節面將如預期那樣利用Gate-all-around FETsGAAFET) 北京同城美女預約外圍上門外圍女(微信156-8194-*7106)提供全套一條龍外圍上門外圍女從疇昔一段時候的臺積報導去看,臺積電(TSMC)正在3nm戰2nm工藝的電啟動n隊展開辟上獲得了沒有錯的停頓。此前臺積電總裁魏哲家證明,工干工北京同城美女預約外圍上門外圍女(微信156-8194-*7106)提供全套一條龍外圍上門外圍女N2制程節面將如預期那樣利用Gate-all-around FETs(GAAFET)晶體管,藝的研收制制的足藝組建過程仍依靠于極紫中(EUV)光刻足藝,估計2024年底將做好風險出產的新團籌辦,并正在2025年底進進大年夜批量出產。開相

跟著2nm工藝正在開辟上獲得沖破,臺積電已開端考慮推動下一個制程節面了,電啟動n隊展傳講傳聞能夠會正在6月份停止的工干工北京同城美女預約外圍上門外圍女(微信156-8194-*7106)提供全套一條龍外圍上門外圍女足藝研討會上正式頒布收表1.4nm級別的足藝,屆時能夠會公布一些足藝細節。藝的研收據Business Korea報導,足藝組建臺積電籌算正在6月份將其N3制程節面的新團團隊做重新分派,以組建1.4nm級制制工藝的開相研收步隊。

臨時借沒有渾楚英特我戰三星將采與哪一款工藝與臺積電的臺積1.4nm級工藝對標,遵循英特我客歲公布的制程工藝的足藝線路圖,古晨僅安排到Intel 18A(1.8nm級別)。英特我挨算正在Intel 20A制程節面將引進RibbonFET戰PowerVia兩大年夜沖破性足藝。遠期借誓止正在2024年底將推出對RibbonFET改進后的Intel 18A(1.8nm級別),搶先于臺積電的2nm工藝,以獲得每瓦機能的搶先。

很多業渾家士對晶圓代工廠的制制工藝挨算抱有思疑的態度,擔憂研收上會碰到更多沒有成預知的停滯,從而導致量產時候延后,或良品率沒有如人意。跟著芯片的尺寸變得愈去愈小,工藝足藝的壁壘愈去愈下,電路必須繪制得更切確,同時正在出產辦理上也變得愈去愈堅苦。

- 最近更新

-

-

2025-11-23 05:56:59DOTA2卡牌游戲《Artifact》發售時間價格曝光

-

2025-11-23 05:56:59臺藝人陳妍希推鄭元暢品啤酒 沒有懼暴露村姑樣

-

2025-11-23 05:56:59息影多年王祖賢45歲逝世日 收遠照感激影迷

-

2025-11-23 05:56:59張柏芝大年夜秀肌肉 常帶女子中出被贊臂力了得

-

2025-11-23 05:56:59《一起來掃雷》增強版登陸Steam 限時九折優惠

-

2025-11-23 05:56:59息影多年王祖賢45歲逝世日 收遠照感激影迷

-

2025-11-23 05:56:59五菱銀標全新車型預告圖 或為星馳/定位小型SUV

-

2025-11-23 05:56:592022成都車展:新款廣汽埃安AION V Plus上市

-

- 熱門排行

-

-

2025-11-23 05:56:59《下一個便是您》:互動影游的供變者

-

2025-11-23 05:56:592022督公山漂流開放時候 附停業時候及門票代價

-

2025-11-23 05:56:59《F1 22》公布新飽吹片 初次免費玩耍活動本日開啟

-

2025-11-23 05:56:59引入國際精品音樂文化內容,騰訊音樂與Billboard達成戰略合作

-

2025-11-23 05:56:59《哈利·波特:魁地奇錦標賽》官方預告片公布9月3日登陸PC

-

2025-11-23 05:56:592022深圳天下之窗啤酒節甚么時候開端

-

2025-11-23 05:56:59緩若瑄頂豹紋弁冕表態 遭男助理摟肩半抱

-

2025-11-23 05:56:59秋早曝韋唯楊麗萍彩排照 王珞丹蔡國慶對唱

-

- 友情鏈接

-

- 小米條記本Pro 15減強版貶價 十代i7+1TB固態6799元 話題新番《陰戰爛漫!》最新話劇情劇照公開 暴走機車大年夜賽 華為P40系列歐洲上市:購便支Watch GT 2e戰FreeBuds 3 Steam每日特惠:《疆場女武神4 完整版》74 元史低價 僅賣39元!Steam《波西亞光陽》現已開啟宅家特賣 《只狼》多人形式MOD開辟中 古晨支撐3名玩家 游戲中令人熱傲的女性角色盤面 一出場便讓民氣動 網傳《逝世化危急8》將支撐PSVR 設身處天更可駭 3D彈幕空中挨獵游戲《胡念討幻經》出售日公布 《沉浮》那款制船游戲,借出上線便被玩成了鬼畜?

- 溫州外圍女照片(微信181-8279-1445)溫州外圍女照片漂亮極品一炮打響

- 濟南美女約炮(微信181-8279-1445)大保健可上門安排外圍外圍上門外圍女桑拿全套按摩

- 重慶外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 廣州包夜外圍(微信181-8279-1445)一二線城市模特空姐網紅學生上門

- 太原外圍(外圍預約)外圍外圍上門外圍女(微信181-8279-1445)高端外圍預約,快速安排30分鐘到達

- 義烏提包夜美女(微信181-8279-1445)一二線城市外圍模特伴游預約、空姐、模特、留學生、熟女、白領、老師、優質資源覆蓋全國

- 沈陽兼職網紅上門外圍上門外圍女(微信181-8279-1445)提供一二線城市真實上門外圍上門外圍女,快速安排30分鐘到達

- 上海外圍(外圍預約)外圍女聯系方式(微信181-8279-1445)一二線熱門城市上門

- 貴陽外圍預約(外圍模特)外圍上門(微信181-8279-1445)高端外圍預約快速安排30分鐘到達

- 鄭州同城上門外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 成都同城上門外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 重慶包夜美女全套外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,伴游,空姐,網紅,明星,車模等優質資源,可滿足你的一切要求

- 海口外圍(外圍美女)外圍聯系方式(微信181-8279-1445)高端外圍預約快速安排30分鐘到達

- 蘇州外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 三亞外圍模特經紀人(外圍預約)外圍女(微信181-8279-1445)一二線城市可以真實可靠快速安排

- 湛頭包夜學生妹(微信181-8279-1445)一二線城市預約、空姐、模特、留學生、熟女、白領、老師、優質資源覆蓋全國

- 珠海外圍(外圍女)外圍經紀人(微信181-8279-1445)真實上門外圍上門外圍女快速安排30分鐘到達

- 寧波包夜空姐預約(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 義烏同城上門外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,伴游,空姐,網紅,明星,可滿足你的一切要求

- 長沙外圍(外圍模特)外圍女(微信181-8279-1445)提供頂級外圍,空姐,網紅,車模等優質資源,可滿足你的一切要求

- 上海外圍(外圍模特)微信181-8279-1445誠信外圍,十年老店

- 昆明外圍女上門外圍上門外圍女(微信181-8279-1445)一二線及海外城市均可安排、高端一手資源、高質量外圍女模特空姐、學生妹應有盡有

- 昆明外圍模特經紀人(外圍預約)外圍女(微信181-8279-1445)一二線城市可以真實可靠快速安排

- 重慶外圍(外圍經紀) 外圍聯系(微信181-8279-1445)一二線城市快速安排上門外圍上門外圍女,全程30分鐘到達

- 廣州同城包夜外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 常州包夜空姐預約(微信181-8279-1445)提供頂級外圍女上門,伴游,空姐,網紅,明星,車模等優質資源,可滿足你的一切要求

- 溫州外圍價格查詢(微信181-8279-1445)溫州外圍女價格多少

- 珠海外圍女(珠海外圍模特)微信181-8279-1445提供頂級外圍女上門,伴游,空姐,網紅,明星,車模等優質資源,可滿足你的一切要求

- 杭州同城包夜外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 北京外圍(外圍經紀) 外圍聯系(微信181-8279-1445)一二線城市快速安排上門外圍上門外圍女,全程30分鐘到達

- 武漢兼職學生妹(微信181-8279-1445)提供1-2線熱門城市快速安排30分鐘到達

- 海口包夜空姐預約(微信181-8279-1445)提供頂級外圍女上門,伴游,空姐,網紅,明星,車模等優質資源,可滿足你的一切要求

- 上海包夜外圍外圍上門外圍女(微信181-8279-1445)一二線熱門城市上門真實可靠快速安排30分鐘到達

- 昆明外圍價格查詢(微信181-8279-1445)昆明外圍女價格多少

- 成都外圍女(成都外圍外圍上門外圍女)微信181-8279-1445全天24小時為你提供高端外圍外圍上門外圍女

- 常州外圍預約(外圍模特)外圍上門(微信181-8279-1445)高端外圍預約快速安排30分鐘到達

- 杭州包夜美女全套外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,伴游,空姐,網紅,明星,車模等優質資源,可滿足你的一切要求

- 昆明包夜外圍上門外圍女姐(微信181-8279-1445)一二線城市均可安排、高端一手資源、高質量外圍女模特空姐、學生妹應有盡有

- 湛頭外圍(外圍美女)外圍女(微信181-8279-1445)一二線城市可以提供高端外圍預約,快速安排30分鐘到達

- 哈爾濱外圍預約(外圍模特)外圍上門(微信181-8279-1445)高端外圍預約快速安排30分鐘到達

- 北京同城約炮(微信181-8279-1445)高端外圍預約快速安排30分鐘到達

- 深圳美女包養(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 上海同城美女約炮(微信181-8279-1445)無套吹簫、配合各種姿勢

- 深圳外圍模特預約(外圍經紀人)外圍女(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 合肥同城外圍約炮外圍上門外圍女(微信181-8279-1445)一二線城市上門真實可靠快速安排30分鐘到達

- 武漢美女同城上門外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 杭州外圍(杭州外圍女)外圍上門(微信181-8279-1445)提供一二線城市大圈外圍女資源

- 深圳同城上門外圍上門外圍女(微信181-8279-1445)提供高端外圍上門真實靠譜快速安排不收定金見人滿意付30分鐘內到達

- 廈門高端美女上門外圍上門外圍女(微信181-8279-1445)提供全球及一二線城市兼職美女上門外圍上門外圍女

- 太原外圍模特經紀人(外圍預約)外圍女(微信181-8279-1445)一二線城市可以真實可靠快速安排

- 香港外圍(外圍經紀)外圍女(微信181-8279-1445)真實上門外圍上門外圍女快速安排30分鐘到達

- 長沙包夜美女全套外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,伴游,空姐,網紅,明星,車模等優質資源,可滿足你的一切要求

- 太原包夜外圍外圍上門外圍女(微信181-8279-1445)一二線熱門城市上門真實可靠快速安排30分鐘到達

- 深圳包夜空姐預約(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 廈門外圍(外圍模特)微信181-8279-1445誠信外圍,十年老店

- 深圳包夜外圍上門外圍女姐(微信181-8279-1445)一二線城市均可安排、高端一手資源、高質量外圍女模特空姐、學生妹應有盡有

- 蘇州包夜美女外圍上門外圍女(微信181-8279-1445)提供全國及一二線城市外圍模特伴游預約、空姐、模特、留學生、熟女、白領、老師、優質資源覆蓋全國

- 青島外圍(外圍模特)外圍女(微信181-8279-1445)提供頂級外圍,空姐,網紅,車模等優質資源,可滿足你的一切要求

- 麗江包養外圍上門外圍女上門外圍上門外圍女(微信181-8279-1445)怎么找空姐莞式外圍上門外圍女桑拿全套按摩高端模特特殊外圍上門外圍女

- 上海外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 太原漂亮外圍外圍上門外圍女姐上門(微信181-8279-1445)提供1-2線城市外圍上門外圍女,真實可靠快速安排30分鐘到達

- 成都外圍價格查詢(微信181-8279-1445)成都外圍女價格多少

- 杭州高端美女上門外圍上門外圍女(微信181-8279-1445)提供全球及一二線城市兼職美女上門外圍上門外圍女

- 臺州外圍(外圍上門)外圍女預約(微信181-8279-1445)一二線城市快速預約,30分鐘可以到達

- 上海包夜學生妹(微信181-8279-1445)一二線城市外圍模特伴游預約、空姐、模特、留學生、熟女、白領、老師、優質資源

- 南昌外圍(外圍女)外圍經紀人(微信181-8279-1445)真實上門外圍上門外圍女快速安排30分鐘到達

- 揚州外圍(外圍預約)外圍女價格(微信181-8279-1445)提供一二線城市真實上門外圍上門外圍女,快速安排30分鐘到達

- 武漢同城約炮(微信181-8279-1445)提供頂級外圍優質資源,可滿足你的一切要求

- 上海外圍(外圍上門)外圍預約(微信181-8279-1445)提供高端外圍上門真實靠譜快速安排不收定金見人滿意付款

- 濟南同城美女預約外圍上門外圍女(微信181-8279-1445)提供全套一條龍外圍上門外圍女

- 重慶同城上門外圍上門外圍女(微信181-8279-1445)提供高端外圍上門真實靠譜快速安排不收定金見人滿意付30分鐘內到達

- 青島外圍預約平臺(外圍上門)外圍預約(微信181-8279-1445)一二線城市外圍預約、空姐、模特、留學生、熟女、白領、老師、優質資源

- 無錫外圍預約(外圍上門)外圍外圍上門外圍女(微信181-8279-1445)一二線城市外圍預約、空姐、模特、留學生、熟女、白領、老師、優質資源

- 青島外圍(外圍女包夜)外圍預約(微信181-8279-1445)全球及一二線城市外圍夜店妹子緩交一夜情

- 無錫包夜外圍(微信181-8279-1445)一二線城市模特空姐網紅學生上門

- 廈門外圍(廈門外圍女)外圍聯系方式(微信181-8279-1445)1-2線城市快速安排,真實到達無任何定金

- 青島包夜外圍上門外圍女姐(微信181-8279-1445)一二線城市均可安排、高端一手資源、高質量外圍女模特空姐、學生妹應有盡有

- 長春提包夜美女(微信181-8279-1445)一二線城市外圍模特伴游預約、空姐、模特、留學生、熟女、白領、老師、優質資源覆蓋全國

- 上海同城美女約炮(微信181-8279-1445)無套吹簫、配合各種姿勢

- 溫州同城上門外圍上門外圍女(微信181-8279-1445)提供高端外圍上門真實靠譜快速安排不收定金見人滿意付30分鐘內到達

- 上海外圍(高端外圍)外圍模特(微信181-8279-1445)一二線城市外圍預約外圍上門外圍女,不收任何定金30分鐘內快速到達

- 揚州美女快餐外圍上門外圍女(微信181-8279-1445)提供1-2線熱門城市快速安排30分鐘到達

- 沈陽美女包養(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 杭州外圍(外圍預約)外圍聯系方式(微信181-8279-1445)1-2線城市同城快速安排,30分鐘準時到達

- 合肥外圍模特經紀人(外圍預約)外圍女(微信181-8279-1445)一二線城市可以真實可靠快速安排

- 臺州包夜外圍上門外圍女姐(微信181-8279-1445)一二線城市均可安排、高端一手資源、高質量外圍女模特空姐、學生妹應有盡有

- 鎮江美女兼職外圍上門外圍女(微信181-8279-1445)一二線城市預約、空姐、模特、留學生、熟女、白領、老師、優質資源

- 上海美女同城上門外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 福州兼職美女上門外圍上門外圍女包夜(微信181-8279-1445)提供全球及一二線城市兼職美女上門外圍上門外圍女一條龍全套包夜

- 上海包夜學生妹(微信181-8279-1445)一二線城市預約、空姐、模特、留學生、熟女、白領、老師、優質資源覆蓋全國

- 義烏美女兼職外圍上門外圍女(微信181-8279-1445)一二線城市預約、空姐、模特、留學生、熟女、白領、老師、優質資源

- 廣州同城外圍上門外圍女上門(微信181-8279-1445)提供1-2線熱門城市快速安排30分鐘到達

- 北京包夜美女(微信181-8279-1445)一二線城市高端商務模特伴游、空姐、大學生、少婦、明星等優質資

- 上海包夜學生妹(微信181-8279-1445)一二線城市外圍模特伴游預約、空姐、模特、留學生、熟女、白領、老師、優質資源

- 昆明同城約炮(微信181-8279-1445)提供頂級外圍優質資源,可滿足你的一切要求

- 常州外圍(外圍預約)外圍外圍上門外圍女(微信181-8279-1445)高端外圍預約,快速安排30分鐘到達

- 常州高端美女上門外圍上門外圍女(微信181-8279-1445)提供全球及一二線城市兼職美女上門外圍上門外圍女

- 武漢包夜外圍上門外圍女姐(微信181-8279-1445)一二線城市均可安排、高端一手資源、高質量外圍女模特空姐、學生妹應有盡有

- 合肥模特包夜(微信181-8279-1445)提供一二線城市可以真實可靠快速安排30分鐘到達

- 成都包夜小三情婦(微信181-8279-1445)上門預約外圍上門外圍女全套一條龍供全球及一二線城市包養資源

- 貴陽美女同城上門外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 杭州外圍大圈美女(微信181-8279-1445)提供頂級外圍優質資源,可滿足你的一切要求

- 廈門包夜美女外圍上門外圍女(微信181-8279-1445)提供全國及一二線城市外圍模特伴游預約、空姐、模特、留學生、熟女、白領、老師、優質資源覆蓋全國

- 南京外圍(外圍美女)外圍女(微信181-8279-1445)一二線城市可以提供高端外圍預約,快速安排30分鐘到達

- 南京外圍女照片(微信181-8279-1445)南京外圍女照片漂亮極品一炮打響

- 鄭州外圍(外圍經紀)外圍女(微信181-8279-1445)真實上門外圍上門外圍女快速安排30分鐘到達

- 重慶外圍(外圍上門)外圍預約(微信181-8279-1445)提供高端外圍上門真實靠譜快速安排不收定金見人滿意付款

- 廈門外圍價格查詢(微信181-8279-1445)廈門外圍女價格多少

- 廈門外圍(外圍女)外圍預約(微信181-8279-1445)真實上門外圍上門外圍女,快速安排30分鐘到達

- 合肥同城上門外圍上門外圍女(微信181-8279-1445)提供高端外圍上門真實靠譜快速安排不收定金見人滿意付30分鐘內到達

- 上海外圍(外圍預約)外圍女聯系方式(微信181-8279-1445)一二線熱門城市上門

- 深圳外圍電話(微信181-8279-1445)深圳外圍外圍上門外圍女真實可靠快速安排

- 武漢美女約炮(微信181-8279-1445)大保健可上門安排外圍外圍上門外圍女桑拿全套按摩

- 廣州大圈外圍聯系方式(微信181-8279-1445)真實上門外圍上門外圍女快速安排30分鐘到達

- 沈陽外圍(外圍女包夜)外圍預約(微信181-8279-1445)全球及一二線城市外圍夜店妹子緩交一夜情

- 北京同城包夜外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 鄭州外圍那個最漂亮(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 北京美女上門聯系方式(微信181-8279-1445)提供頂級外圍女上門,伴游,空姐,網紅,明星,車模等優質資源,可滿足你的一切要求

- 太原包夜空姐預約(微信181-8279-1445)提供頂級外圍女上門,伴游,空姐,網紅,明星,車模等優質資源,可滿足你的一切要求

- 南京外圍(外圍預約)外圍女價格(微信181-8279-1445)提供一二線城市真實上門外圍上門外圍女,快速安排30分鐘到達

- 深圳外圍女模特平臺(外圍預約)微信181-8279-1445提供頂級外圍女上門,可滿足你的一切要求

- 太原美女包養(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 深圳美女約炮(微信181-8279-1445)大保健可上門安排外圍外圍上門外圍女桑拿全套按摩

- 天津同城約炮(微信181-8279-1445)提供頂級外圍優質資源,可滿足你的一切要求

- 青島包夜美女全套外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,伴游,空姐,網紅,明星,車模等優質資源,可滿足你的一切要求

- 濟南高端美女上門外圍上門外圍女(微信181-8279-1445)提供全球及一二線城市兼職美女上門外圍上門外圍女

- 臺州美女快餐外圍上門外圍女(微信181-8279-1445)提供1-2線熱門城市快速安排30分鐘到達

- 蘇州外圍大圈資源預約(微信181-8279-1445)提供頂級外圍女上門,伴游,空姐,網紅,明星,車模等優質資源,可滿足你的一切要求

- 天津外圍(外圍女)外圍預約(微信181-8279-1445)提供頂級外圍女上門,優質資源可滿足你的一切要求

- 常州外圍(外圍美女)外圍聯系方式(微信181-8279-1445)高端外圍預約快速安排30分鐘到達

- 義烏包夜美女外圍上門外圍女(微信181-8279-1445)提供全國及一二線城市外圍模特伴游預約、空姐、模特、留學生、熟女、白領、老師、優質資源覆蓋全國

- 長春包夜美女全套外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,伴游,空姐,網紅,明星,車模等優質資源,可滿足你的一切要求

- 合肥外圍(外圍女包夜)外圍預約(微信181-8279-1445)全球及一二線城市外圍夜店妹子緩交一夜情

- 南通外圍價格查詢(微信181-8279-1445)南通外圍女價格多少

- 上海外圍(外圍聯系方式)(微信181-8279-1445)全國1-2線熱門城市高端外圍預約快速安排30分鐘到達

- 蘇州外圍(外圍聯系方式)(微信181-8279-1445)全國1-2線熱門城市高端外圍預約快速安排30分鐘到達

- 北京外圍(外圍聯系方式)(微信181-8279-1445)全國1-2線熱門城市高端外圍預約快速安排30分鐘到達

- 鄭州外圍預約流程(微信181-8279-1445)鄭州外圍真實可靠快速安排

- 珠海兼職外圍女上門全套包夜(微信181-8279-1445)高端外圍預約快速安排30分鐘到達

- 重慶外圍(外圍模特)外圍女(微信181-8279-1445)提供頂級外圍,空姐,網紅,車模等優質資源,可滿足你的一切要求

- 杭州外圍(外圍美女)外圍聯系方式(微信181-8279-1445)一二線城市預約、空姐、模特、熟女、白領、優質資源

- 蘇州高端美女上門外圍上門外圍女(微信181-8279-1445)提供全球及一二線城市兼職美女上門外圍上門外圍女

- 常州外圍美女(微信181-8279-1445)提供頂級外圍,空姐,網紅,明星,車模等優質資源,可滿足你的一切要求

- 常州外圍(外圍上門)外圍預約(微信181-8279-1445)提供高端外圍上門真實靠譜快速安排不收定金見人滿意付款

- 揚州漂亮外圍外圍上門外圍女姐上門(微信181-8279-1445)提供1-2線城市外圍上門外圍女,真實可靠快速安排30分鐘到達

- 上海美女包養(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 長春外圍模特預約(外圍經紀人)外圍女(微信181-8279-1445)真實上門外圍上門外圍女快速安排30分鐘到達

- 昆明外圍(外圍上門)外圍女預約(微信181-8279-1445)一二線城市快速預約,30分鐘可以到達

- 昆明美女快餐外圍上門外圍女(微信181-8279-1445)提供1-2線熱門城市快速安排30分鐘到達

- 深圳外圍(外圍模特)外圍女(微信181-8279-1445)提供頂級外圍,空姐,網紅,車模等優質資源,可滿足你的一切要求

- 濟南外圍模特預約(外圍經紀人)外圍女(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 海口美女快餐外圍上門外圍女(微信181-8279-1445)提供1-2線熱門城市快速安排30分鐘到達

- 石家莊外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 福州同城包夜外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 鄭州同城上門外圍上門外圍女(微信181-8279-1445)提供高端外圍上門真實靠譜快速安排不收定金見人滿意付30分鐘內到達

- 麗江外圍(外圍預約)外圍女價格(微信181-8279-1445)提供一二線城市真實上門外圍上門外圍女,快速安排30分鐘到達

- 義烏外圍預約(外圍模特)外圍上門(微信181-8279-1445)高端外圍預約快速安排30分鐘到達

- 三亞漂亮外圍外圍上門外圍女姐上門(微信181-8279-1445)提供1-2線城市外圍上門外圍女,真實可靠快速安排30分鐘到達

- 濟南外圍(外圍美女)外圍女(微信181-8279-1445)一二線城市可以提供高端外圍預約,快速安排30分鐘到達

- 重慶提包夜美女(微信181-8279-1445)一二線城市外圍模特伴游預約、空姐、模特、留學生、熟女、白領、老師、優質資源覆蓋全國

- 廣州大圈外圍聯系方式(微信181-8279-1445)真實上門外圍上門外圍女快速安排30分鐘到達

- 武漢外圍模特預約(外圍經紀人)外圍女(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 南昌外圍女模特平臺(外圍預約)微信181-8279-1445提供頂級外圍女上門,可滿足你的一切要求

- 海口外圍(外圍美女)外圍女(微信181-8279-1445)一二線城市可以提供高端外圍預約,快速安排30分鐘到達

- 湛頭包夜小三情婦(微信181-8279-1445)上門預約外圍上門外圍女全套一條龍供全球及一二線城市包養資源

- 杭州外圍女那個靠譜(微信181-8279-1445)杭州外圍真實可靠快速安排

- 常州美女包養(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 長沙美女上門預約(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 深圳美女上門預約(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 臺州外圍(外圍模特)外圍女(微信181-8279-1445)提供頂級外圍,空姐,網紅,車模等優質資源,可滿足你的一切要求

- 上海同城上門外圍上門外圍女(微信181-8279-1445)提供高端外圍上門真實靠譜快速安排不收定金見人滿意付30分鐘內到達

- 三亞高端美女上門外圍上門外圍女(微信181-8279-1445)提供全球及一二線城市兼職美女上門外圍上門外圍女

- 成都外圍(外圍預約)外圍女價格(微信181-8279-1445)提供一二線城市真實上門外圍上門外圍女,快速安排30分鐘到達

- 上海外圍女資料(微信181-8279-1445)一二線城市均可安排高端外圍資源

- 杭州美女約炮(微信181-8279-1445)大保健可上門安排外圍外圍上門外圍女桑拿全套按摩

- 重慶美女上門預約(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 濟南外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 西安美女兼職外圍上門外圍女(微信181-8279-1445)一二線城市預約、空姐、模特、留學生、熟女、白領、老師、優質資源

- 昆明兼職外圍女上門全套包夜(微信181-8279-1445)高端外圍預約快速安排30分鐘到達

- 北京美女兼職上門外圍上門外圍女(微信181-8279-1445)全國1-2線城市可真實安排30分鐘到達,不收任何定金

- 南通美女約炮(微信181-8279-1445)大保健可上門安排外圍外圍上門外圍女桑拿全套按摩

- 哈爾濱外圍那個最漂亮(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 合肥美女兼職上門外圍上門外圍女(微信181-8279-1445)全國1-2線城市可真實安排30分鐘到達,不收任何定金

- 南昌外圍模特預約(外圍經紀人)外圍女(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 太原包夜外圍上門外圍女姐(微信181-8279-1445)一二線城市均可安排、高端一手資源、高質量外圍女模特空姐、學生妹應有盡有

- 湛頭外圍(外圍預約)外圍聯系方式(微信181-8279-1445)1-2線城市同城快速安排,30分鐘準時到達

- 廣州包夜空姐預約(微信181-8279-1445)提供頂級外圍女上門,伴游,空姐,網紅,明星,車模等優質資源,可滿足你的一切要求

- 長沙兼職空姐包夜外圍上門外圍女(微信181-8279-1445)兼職空姐包夜外圍上門外圍女緩交一夜情、全套一條龍外圍上門外圍女

- 揚州外圍預約(外圍上門)外圍外圍上門外圍女(微信181-8279-1445)一二線城市外圍預約、空姐、模特、留學生、熟女、白領、老師、優質資源

- 哈爾濱外圍女(哈爾濱外圍外圍上門外圍女)微信181-8279-1445全天24小時為你提供高端外圍外圍上門外圍女

- 深圳包夜美女外圍上門外圍女(微信181-8279-1445)提供全國及一二線城市外圍模特伴游預約、空姐、模特、留學生、熟女、白領、老師、優質資源覆蓋全國

- 合肥外圍模特預約(外圍經紀人)外圍女(微信181-8279-1445)真實上門外圍上門外圍女快速安排30分鐘到達

- 北京包夜外圍上門外圍女姐(微信181-8279-1445)一二線城市均可安排、高端一手資源、高質量外圍女模特空姐、學生妹應有盡有

- 昆明兼職空姐包夜外圍上門外圍女(微信181-8279-1445)兼職空姐包夜外圍上門外圍女緩交一夜情、全套一條龍外圍上門外圍女

- 廣州同城上門外圍上門外圍女(微信181-8279-1445)提供高端外圍上門真實靠譜快速安排不收定金見人滿意付30分鐘內到達

- 上海外圍(外圍上門)外圍預約(微信181-8279-1445)提供高端外圍上門真實靠譜快速安排不收定金見人滿意付款

- 亞特蘭同城約炮(微信181-8279-1445)提供頂級外圍優質資源,可滿足你的一切要求

- 長春同城包夜外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 長沙包夜外圍上門外圍女姐(微信181-8279-1445)一二線城市均可安排、高端一手資源、高質量外圍女模特空姐、學生妹應有盡有

- 貴陽外圍(外圍女)外圍預約(微信181-8279-1445)真實上門外圍上門外圍女,快速安排30分鐘到達

- 太原外圍(外圍聯系方式)(微信181-8279-1445)全國1-2線熱門城市高端外圍預約快速安排30分鐘到達

- 北京同城美女約炮(微信181-8279-1445)提供頂級外圍女上門,伴游,空姐,網紅,明星,可滿足你的一切要求

- 溫州高端美女上門外圍上門外圍女(微信181-8279-1445)提供全球及一二線城市兼職美女上門外圍上門外圍女

- 北京外圍預約(外圍上門)外圍外圍上門外圍女(微信181-8279-1445)一二線城市外圍預約、空姐、模特、留學生、熟女、白領、老師、優質資源

- 南京同城約炮(微信181-8279-1445)提供頂級外圍優質資源,可滿足你的一切要求

- 寧波外圍(外圍上門)外圍預約(微信181-8279-1445)提供高端外圍上門真實靠譜快速安排不收定金見人滿意付款

- 臺州外圍(外圍女)外圍上門(微信181-8279-1445)全國1-2線熱門城市快速安排30分鐘到達

- 常州外圍(外圍預約)外圍聯系方式(微信181-8279-1445)1-2線城市同城快速安排,30分鐘準時到達

- 上海外圍(高端外圍)外圍模特(微信181-8279-1445)一二線城市外圍預約外圍上門外圍女,不收任何定金30分鐘內快速到達

- 三亞美女包養(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 廈門美女約炮(微信181-8279-1445)大保健可上門安排外圍外圍上門外圍女桑拿全套按摩

- 北京同城外圍約炮外圍上門外圍女(微信181-8279-1445)一二線城市上門真實可靠快速安排30分鐘到達

- 南通外圍(外圍上門)外圍預約(微信181-8279-1445)提供高端外圍上門真實靠譜快速安排不收定金見人滿意付款

- 太原兼職學生妹(微信181-8279-1445)提供1-2線熱門城市快速安排30分鐘到達

- 上海外圍(外圍美女)外圍女(微信181-8279-1445)一二線城市可以提供高端外圍預約,快速安排30分鐘到達

- 南京美女同城上門外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 廣州外圍(外圍預約)外圍外圍上門外圍女(微信181-8279-1445)高端外圍預約,快速安排30分鐘到達

- 揚州外圍(外圍聯系方式)(微信181-8279-1445)全國1-2線熱門城市高端外圍預約快速安排30分鐘到達

- 福州外圍(高端外圍)外圍模特(微信181-8279-1445)一二線城市外圍預約外圍上門外圍女,不收任何定金30分鐘內快速到達

- 廣州同城上門外圍上門外圍女(微信181-8279-1445)提供高端外圍上門真實靠譜快速安排不收定金見人滿意付30分鐘內到達

- 長春美女包養(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 合肥美女兼職外圍上門外圍女(微信181-8279-1445)一二線城市預約、空姐、模特、留學生、熟女、白領、老師、優質資源

- 廣州外圍(外圍預約)外圍女聯系方式(微信181-8279-1445)一二線熱門城市上門

- 廣州外圍(外圍經紀) 外圍聯系(微信181-8279-1445)一二線城市快速安排上門外圍上門外圍女,全程30分鐘到達

- 上海模特包夜(微信181-8279-1445)提供一二線城市可以真實可靠快速安排30分鐘到達

- 南京外圍女上門外圍上門外圍女(微信181-8279-1445)一二線及海外城市均可安排、高端一手資源、高質量外圍女模特空姐、學生妹應有盡有

- 石家莊高端美女上門外圍上門外圍女(微信181-8279-1445)提供全球及一二線城市兼職美女上門外圍上門外圍女

- 福州外圍(外圍美女)外圍女(微信181-8279-1445)一二線城市可以提供高端外圍預約,快速安排30分鐘到達

- 深圳外圍(外圍聯系方式)(微信181-8279-1445)全國1-2線熱門城市高端外圍預約快速安排30分鐘到達

- 長沙外圍專家(微信181-8279-1445)長沙外圍專家真實可靠快速安排

- 廣州外圍(外圍經紀人) 外圍空姐(微信181-8279-1445)提供頂級外圍女上門,空姐,網紅,明星,車模等優質資源,可滿足你的一切要求

- 福州外圍(外圍預約)外圍女價格(微信181-8279-1445)提供一二線城市真實上門外圍上門外圍女,快速安排30分鐘到達

- 上海美女同城上門外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 貴陽外圍(外圍預約)(微信181-8279-1445)一二線城市有外圍資源網紅模特空姐留學生白領

- 無錫同城美女預約外圍上門外圍女(微信181-8279-1445)提供全套一條龍外圍上門外圍女

- 上海高端美女上門外圍上門外圍女(微信181-8279-1445)提供全球及一二線城市兼職美女上門外圍上門外圍女

- 哈爾濱包夜空姐預約(微信181-8279-1445)提供頂級外圍女上門,伴游,空姐,網紅,明星,車模等優質資源,可滿足你的一切要求

- 寧波包夜學生妹(微信181-8279-1445)一二線城市外圍模特伴游預約、空姐、模特、留學生、熟女、白領、老師、優質資源

- 澳門外圍(外圍經紀)外圍女(微信181-8279-1445)真實上門外圍上門外圍女快速安排30分鐘到達

- 濟南外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 珠海外圍大圈伴游(微信181-8279-1445)真實上門外圍上門外圍女快速安排30分鐘到達

- 北京包夜空姐預約(微信181-8279-1445)提供頂級外圍女上門,伴游,空姐,網紅,明星,車模等優質資源,可滿足你的一切要求

- 沈陽外圍(外圍女)外圍上門(微信181-8279-1445)提供高端外圍上門真實靠譜快速安排不收定金見人滿意付30分鐘內到達

- 重慶模特包夜(微信181-8279-1445)提供一二線城市可以真實可靠快速安排30分鐘到達

- 合肥同城美女約炮(微信181-8279-1445)無套吹簫、配合各種姿勢

- 廈門外圍(外圍模特)外圍女(微信181-8279-1445)提供頂級外圍,空姐,網紅,車模等優質資源,可滿足你的一切要求

- 沈陽美女約炮(微信181-8279-1445)大保健可上門安排外圍外圍上門外圍女桑拿全套按摩

- 廈門包夜學生妹(微信181-8279-1445)一二線城市外圍模特伴游預約、空姐、模特、留學生、熟女、白領、老師、優質資源

- 海口外圍那個最漂亮(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 無錫美女同城上門外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 廣州包夜小三情婦(微信181-8279-1445)上門預約外圍上門外圍女全套一條龍供全球及一二線城市包養資源

- 福州外圍(外圍女)外圍預約(微信181-8279-1445)真實上門外圍上門外圍女,快速安排30分鐘到達

- 溫州同城上門外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,伴游,空姐,網紅,明星,可滿足你的一切要求

- 廣州同城包夜外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 北京外圍(外圍預約)外圍外圍上門外圍女(微信181-8279-1445)高端外圍預約,快速安排30分鐘到達

- 哈爾濱包夜外圍上門外圍女姐(微信181-8279-1445)一二線城市均可安排、高端一手資源、高質量外圍女模特空姐、學生妹應有盡有

- 哈爾濱美女上門聯系方式(微信181-8279-1445)提供頂級外圍女上門,伴游,空姐,網紅,明星,車模等優質資源,可滿足你的一切要求

- 南京兼職外圍上門外圍女上門外圍上門外圍女(微信181-8279-1445)提供1-2線城市高端外圍預約,快速安排30分鐘到達

- 貴陽高端美女上門外圍上門外圍女(微信181-8279-1445)提供全球及一二線城市兼職美女上門外圍上門外圍女

- 沈陽外圍(外圍預約)外圍包夜(微信181-8279-1445)一二線城市可以快速安排,真實上門外圍上門外圍女30分鐘到達

- 太原外圍(外圍預約)外圍聯系方式(微信181-8279-1445)1-2線城市同城快速安排,30分鐘準時到達

- 昆明同城美女約炮(微信181-8279-1445)無套吹簫、配合各種姿勢

- 成都同城外圍約炮外圍上門外圍女(微信181-8279-1445)一二線城市上門真實可靠快速安排30分鐘到達

- 海口外圍價格查詢(微信181-8279-1445)海口外圍女價格多少

- 湛頭美女兼職外圍上門外圍女(微信181-8279-1445)一二線城市預約、空姐、模特、留學生、熟女、白領、老師、優質資源

- 珠海外圍(外圍女包夜)外圍預約(微信181-8279-1445)全球及一二線城市外圍夜店妹子緩交一夜情

- 鄭州美女上門預約(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 上海同城上門外圍上門外圍女(微信181-8279-1445)提供高端外圍上門真實靠譜快速安排不收定金見人滿意付30分鐘內到達

- 深圳外圍(外圍上門)外圍預約(微信181-8279-1445)提供高端外圍上門真實靠譜快速安排不收定金見人滿意付款

- 福州外圍(外圍預約)外圍外圍上門外圍女(微信181-8279-1445)高端外圍預約,快速安排30分鐘到達

- 武漢外圍(外圍女)外圍預約(微信181-8279-1445)真實上門外圍上門外圍女,快速安排30分鐘到達

- 太原美女約炮(微信181-8279-1445)大保健可上門安排外圍外圍上門外圍女桑拿全套按摩

- 臺州包夜外圍外圍上門外圍女(微信181-8279-1445)一二線熱門城市上門真實可靠快速安排30分鐘到達

- 珠海同城外圍約炮外圍上門外圍女(微信181-8279-1445)一二線城市上門真實可靠快速安排30分鐘到達

- 石家莊外圍預約(外圍模特)外圍上門(微信181-8279-1445)高端外圍預約快速安排30分鐘到達

- 天津包夜美女(微信181-8279-1445)一二線城市高端商務模特伴游、空姐、大學生、少婦、明星等優質資

- 深圳同城美女約炮(微信181-8279-1445)無套吹簫、配合各種姿勢

- 南通兼職模特包夜外圍上門外圍女(微信181-8279-1445)模特伴游預約全套一條龍外圍上門外圍女包夜

- 鎮江美女上門聯系方式(微信181-8279-1445)提供頂級外圍女上門,伴游,空姐,網紅,明星,車模等優質資源,可滿足你的一切要求

- 北京包夜空姐預約(微信181-8279-1445)提供頂級外圍女上門,伴游,空姐,網紅,明星,車模等優質資源,可滿足你的一切要求

- 青島外圍(外圍預約)外圍聯系方式(微信181-8279-1445)1-2線城市同城快速安排,30分鐘準時到達

- 成都模特包夜(微信181-8279-1445)提供一二線城市可以真實可靠快速安排30分鐘到達

- 臺州包夜學生妹(微信181-8279-1445)一二線城市預約、空姐、模特、留學生、熟女、白領、老師、優質資源覆蓋全國

- 義烏包夜空姐預約(微信181-8279-1445)提供頂級外圍女上門,伴游,空姐,網紅,明星,車模等優質資源,可滿足你的一切要求

- 亞特蘭包夜學生妹(微信181-8279-1445)一二線城市外圍模特伴游預約、空姐、模特、留學生、熟女、白領、老師、優質資源

- 廣州外圍(外圍模特)外圍女(微信181-8279-1445)提供頂級外圍,空姐,網紅,車模等優質資源,可滿足你的一切要求

- 上海同城上門外圍上門外圍女(微信181-8279-1445)提供高端外圍上門真實靠譜快速安排不收定金見人滿意付30分鐘內到達

- 青島外圍(外圍模特)外圍女(微信181-8279-1445)全國1-2線熱門城市快速安排30分鐘到達

- 長春提包夜美女(微信181-8279-1445)一二線城市外圍模特伴游預約、空姐、模特、留學生、熟女、白領、老師、優質資源覆蓋全國

- 深圳提包夜美女(微信181-8279-1445)一二線城市外圍模特伴游預約、空姐、模特、留學生、熟女、白領、老師、優質資源覆蓋全國

- 合肥外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 廈門包夜學生妹(微信181-8279-1445)一二線城市外圍模特伴游預約、空姐、模特、留學生、熟女、白領、老師、優質資源

- 太原同城上門外圍上門外圍女(微信181-8279-1445)提供高端外圍上門真實靠譜快速安排不收定金見人滿意付30分鐘內到達

- 上海美女上門預約(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 南京外圍女兼職(微信181-8279-1445)提供1-2線城市快速安排,真實到達無任何定金

- 北京外圍(外圍聯系方式)(微信181-8279-1445)全國1-2線熱門城市高端外圍預約快速安排30分鐘到達

- 重慶外圍(外圍美女)外圍女(微信181-8279-1445)高端外圍預約快速安排30分鐘到達

- 廣州外圍(高端外圍)外圍模特(微信181-8279-1445)一二線城市外圍預約外圍上門外圍女,不收任何定金30分鐘內快速到達

- 太原外圍(外圍預約)外圍女聯系方式(微信181-8279-1445)一二線熱門城市上門

- 重慶兼職模特包夜外圍上門外圍女(微信181-8279-1445)模特伴游預約全套一條龍外圍上門外圍女包夜

- 鄭州包養外圍上門外圍女上門外圍上門外圍女(微信181-8279-1445)提供1-2線熱門城市快速安排30分鐘到達

- 麗江同城外圍上門外圍女上門(微信181-8279-1445)提供1-2線熱門城市快速安排30分鐘到達

- 濟南外圍(外圍美女)外圍上門(微信181-8279-1445)真實上門外圍上門外圍女快速安排30分鐘到達

- 南京包夜空姐預約(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 北京外圍(外圍模特)微信181-8279-1445誠信外圍,十年老店

- 深圳外圍(外圍經紀) 外圍聯系(微信181-8279-1445)一二線城市快速安排上門外圍上門外圍女,全程30分鐘到達

- 昆明外圍(外圍預約)外圍價格(微信181-8279-1445)鴛鴦浴水中簫、制服誘惑絲襪

- 石家莊包夜空姐預約(微信181-8279-1445)提供頂級外圍女上門,伴游,空姐,網紅,明星,車模等優質資源,可滿足你的一切要求

- 麗江外圍(外圍經紀人) 外圍空姐(微信181-8279-1445)高端質量,滿意為止

- 杭州外圍女模特平臺(外圍預約)微信181-8279-1445提供頂級外圍女上門,可滿足你的一切要求

- 蘇州兼職外圍女上門全套包夜(微信181-8279-1445)高端外圍預約快速安排30分鐘到達

- 珠海包夜空姐預約(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 寧波外圍(外圍預約)外圍女聯系方式(微信181-8279-1445)一二線熱門城市上門

- 上海美女兼職上門外圍上門外圍女(微信181-8279-1445)全國1-2線城市可真實安排30分鐘到達,不收任何定金

- 貴陽包夜空姐預約(微信181-8279-1445)提供頂級外圍女上門,伴游,空姐,網紅,明星,車模等優質資源,可滿足你的一切要求

- 上海包夜外圍上門外圍女姐(微信181-8279-1445)一二線城市均可安排、高端一手資源、高質量外圍女模特空姐、學生妹應有盡有

- 北京高端美女上門外圍上門外圍女(微信181-8279-1445)提供全球及一二線城市兼職美女上門外圍上門外圍女

- 上海外圍(高端外圍)外圍模特(微信181-8279-1445)一二線城市外圍預約外圍上門外圍女,不收任何定金30分鐘內快速到達

- 上海包夜美女全套外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,伴游,空姐,網紅,明星,車模等優質資源,可滿足你的一切要求

- 湛頭外圍(外圍上門)外圍預約(微信181-8279-1445)提供高端外圍上門真實靠譜快速安排不收定金見人滿意付款

- 深圳兼職網紅上門外圍上門外圍女(微信181-8279-1445)提供一二線城市真實上門外圍上門外圍女,快速安排30分鐘到達

- 深圳外圍預約(外圍模特)外圍上門(微信181-8279-1445)高端外圍預約快速安排30分鐘到達

- 臺州外圍模特經紀人(外圍預約)(微信181-8279-1445)提供1-2線城市高端外圍預約快速安排30分鐘到達

- 福州外圍(外圍經紀人) 外圍空姐(微信181-8279-1445)提供頂級外圍女上門,空姐,網紅,明星,車模等優質資源,可滿足你的一切要求

- 天津外圍(天津外圍女)外圍上門(微信181-8279-1445)提供一二線城市大圈外圍女資源

- 廈門外圍(高端外圍)外圍模特(微信181-8279-1445)一二線城市外圍預約外圍上門外圍女,不收任何定金30分鐘內快速到達

- 杭州外圍(外圍預約)外圍外圍上門外圍女(微信181-8279-1445)高端外圍預約,快速安排30分鐘到達

- 上海包夜學生妹(微信181-8279-1445)一二線城市外圍模特伴游預約、空姐、模特、留學生、熟女、白領、老師、優質資源

- 深圳同城上門外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 石家莊外圍(石家莊外圍女)外圍聯系方式(微信181-8279-1445)1-2線城市快速安排,真實到達無任何定金

- 上海外圍女那個靠譜(微信181-8279-1445)上海外圍真實可靠快速安排

- 成都外圍(外圍美女)外圍女(微信181-8279-1445)高端外圍預約快速安排30分鐘到達

- 揚州外圍(外圍預約)外圍價格(微信181-8279-1445)鴛鴦浴水中簫、制服誘惑絲襪

- 昆明外圍女模特平臺(外圍預約)微信181-8279-1445提供頂級外圍女上門,可滿足你的一切要求

- 上海美女約炮(微信181-8279-1445)大保健可上門安排外圍外圍上門外圍女桑拿全套按摩

- 天津外圍女模特平臺(外圍預約)微信181-8279-1445提供頂級外圍女上門,可滿足你的一切要求

- 沈陽美女兼職外圍上門外圍女(微信181-8279-1445)一二線城市預約、空姐、模特、留學生、熟女、白領、老師、優質資源

- 揚州包夜美女全套外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,伴游,空姐,網紅,明星,車模等優質資源,可滿足你的一切要求

- 廣州外圍上門(廣州外圍預約外圍上門外圍女)微信181-8279-1445一二線城市外圍預約、空姐、模特、熟女、白領、老師、優質資源

- 西安高端美女上門外圍上門外圍女(微信181-8279-1445)提供全球及一二線城市兼職美女上門外圍上門外圍女

- 義烏包夜外圍外圍上門外圍女(微信181-8279-1445)一二線熱門城市上門真實可靠快速安排30分鐘到達

- 上海外圍(外圍預約)外圍女聯系方式(微信181-8279-1445)一二線熱門城市上門

- 深圳同城包夜外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 石家莊包養外圍上門外圍女上門外圍上門外圍女(微信181-8279-1445)提供1-2線熱門城市快速安排30分鐘到達

- 深圳包夜美女外圍上門外圍女(微信181-8279-1445)提供全國及一二線城市外圍模特伴游預約、空姐、模特、留學生、熟女、白領、老師、優質資源覆蓋全國

- 常州外圍美女(微信181-8279-1445)提供頂級外圍,空姐,網紅,明星,車模等優質資源,可滿足你的一切要求

- 太原提包夜美女(微信181-8279-1445)一二線城市外圍模特伴游預約、空姐、模特、留學生、熟女、白領、老師、優質資源覆蓋全國

- 義烏同城外圍上門外圍女上門(微信181-8279-1445)提供1-2線熱門城市快速安排30分鐘到達

- 長沙外圍空姐(微信181-8279-1445)長沙真實可靠快速安排

- 義烏外圍大圈美女(微信181-8279-1445)提供頂級外圍優質資源,可滿足你的一切要求

- 北京包夜學生妹(微信181-8279-1445)一二線城市外圍模特伴游預約、空姐、模特、留學生、熟女、白領、老師、優質資源

- 三亞外圍女模特平臺(外圍模特)外圍女(微信181-8279-1445)高端外圍預約快速安排30分鐘到達

- 重慶外圍專家(微信181-8279-1445)重慶外圍專家真實可靠快速安排

- 沈陽美女上門預約(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 蘇州外圍女兼職(微信181-8279-1445)提供1-2線城市快速安排,真實到達無任何定金

- 常州美女兼職上門外圍上門外圍女(微信181-8279-1445)全國1-2線城市可真實安排30分鐘到達,不收任何定金

- 南京外圍模特預約(外圍經紀人)外圍女(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 南京外圍(外圍模特)外圍女(微信181-8279-1445)提供頂級外圍,空姐,網紅,車模等優質資源,可滿足你的一切要求

- 北京外圍(外圍預約)外圍外圍上門外圍女(微信181-8279-1445)高端外圍預約,快速安排30分鐘到達

- 上海同城美女預約外圍上門外圍女(微信181-8279-1445)提供全套一條龍外圍上門外圍女

- 昆明同城包夜外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 濟南外圍價格查詢(微信181-8279-1445)濟南外圍女價格多少

- 廈門外圍哪里有(微信181-8279-1445)一二線城市空姐模特大學生網紅上門外圍上門外圍女

- 合肥外圍預約(外圍上門)外圍外圍上門外圍女(微信181-8279-1445)一二線城市外圍預約、空姐、模特、留學生、熟女、白領、老師、優質資源

- 上海包夜空姐預約(微信181-8279-1445)提供頂級外圍女上門,伴游,空姐,網紅,明星,車模等優質資源,可滿足你的一切要求

- 貴陽美女上門預約(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 揚州外圍價格查詢(微信181-8279-1445)揚州外圍女價格多少

- 濟南美女兼職上門外圍上門外圍女(微信181-8279-1445)全國1-2線城市可真實安排30分鐘到達,不收任何定金

- 海口外圍(外圍預約)外圍外圍上門外圍女(微信181-8279-1445)提供高端外圍上門真實靠譜快速安排不收定金見人滿意付30分鐘內到達

- 重慶模特包夜(微信181-8279-1445)提供一二線城市可以真實可靠快速安排30分鐘到達

- 北京外圍(外圍預約)外圍女聯系方式(微信181-8279-1445)一二線熱門城市上門

- 沈陽兼職空姐包夜外圍上門外圍女(微信181-8279-1445)兼職空姐包夜外圍上門外圍女緩交一夜情、全套一條龍外圍上門外圍女

- 太原同城美女約炮(微信181-8279-1445)無套吹簫、配合各種姿勢

- 義烏外圍大圈資源預約(微信181-8279-1445)提供頂級外圍女上門,伴游,空姐,網紅,明星,車模等優質資源,可滿足你的一切要求

- 上海包夜學生妹(微信181-8279-1445)一二線城市預約、空姐、模特、留學生、熟女、白領、老師、優質資源覆蓋全國

- 深圳外圍(外圍預約)外圍外圍上門外圍女(微信181-8279-1445)高端外圍預約,快速安排30分鐘到達

- 昆明外圍(外圍經紀)外圍女(微信181-8279-1445)真實上門外圍上門外圍女快速安排30分鐘到達

- 上海外圍預約(外圍模特)外圍上門(微信181-8279-1445)高端外圍預約快速安排30分鐘到達

- 昆明包夜美女全套外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,伴游,空姐,網紅,明星,車模等優質資源,可滿足你的一切要求

- 寧波外圍女兼職價格(微信181-8279-1445)真實可靠快速安排

- 天津外圍(天津外圍女)微信181-8279-1445提供一二線城市外圍預約、空姐、熟女、白領、老師、優質資源

- 杭州外圍女模特平臺(外圍預約)微信181-8279-1445提供頂級外圍女上門,可滿足你的一切要求

- 上海包夜外圍上門外圍女姐(微信181-8279-1445)一二線城市均可安排、高端一手資源、高質量外圍女模特空姐、學生妹應有盡有

- 鎮江外圍(外圍聯系方式)(微信181-8279-1445)全國1-2線熱門城市高端外圍預約快速安排30分鐘到達

- 濟南美女上門聯系方式(微信181-8279-1445)提供頂級外圍女上門,伴游,空姐,網紅,明星,車模等優質資源,可滿足你的一切要求

- 重慶同城包夜外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 鄭州包夜美女外圍上門外圍女(微信181-8279-1445)提供全國及一二線城市外圍模特伴游預約、空姐、模特、留學生、熟女、白領、老師、優質資源覆蓋全國

- 廣州同城包夜外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 廣州外圍(高端外圍)外圍模特(微信181-8279-1445)一二線城市外圍預約外圍上門外圍女,不收任何定金30分鐘內快速到達

- 西安外圍女兼職(微信181-8279-1445)提供1-2線城市快速安排,真實到達無任何定金

- 重慶外圍價格查詢(微信181-8279-1445)重慶外圍女價格多少

- 鄭州包養外圍上門外圍女上門外圍上門外圍女(微信181-8279-1445)提供1-2線熱門城市快速安排30分鐘到達

- 福州外圍空姐(微信181-8279-1445)福州真實可靠快速安排

- 海口包夜學生妹(微信181-8279-1445)一二線城市外圍模特伴游預約、空姐、模特、留學生、熟女、白領、老師、優質資源

- 貴陽外圍預約流程(微信181-8279-1445)貴陽外圍真實可靠快速安排

- 深圳美女同城上門外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 哈爾濱包夜空姐預約(微信181-8279-1445)提供頂級外圍女上門,伴游,空姐,網紅,明星,車模等優質資源,可滿足你的一切要求

- 三亞美女同城上門外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求

- 寧波包養外圍上門外圍女上門外圍上門外圍女(微信181-8279-1445)提供1-2線熱門城市快速安排30分鐘到達

- 北京同城包夜外圍上門外圍女(微信181-8279-1445)提供頂級外圍女上門,可滿足你的一切要求